一文搞懂 | ARM MMU

MMU概念介绍

MMU分为两个部分: TLB maintenance 和 address translation

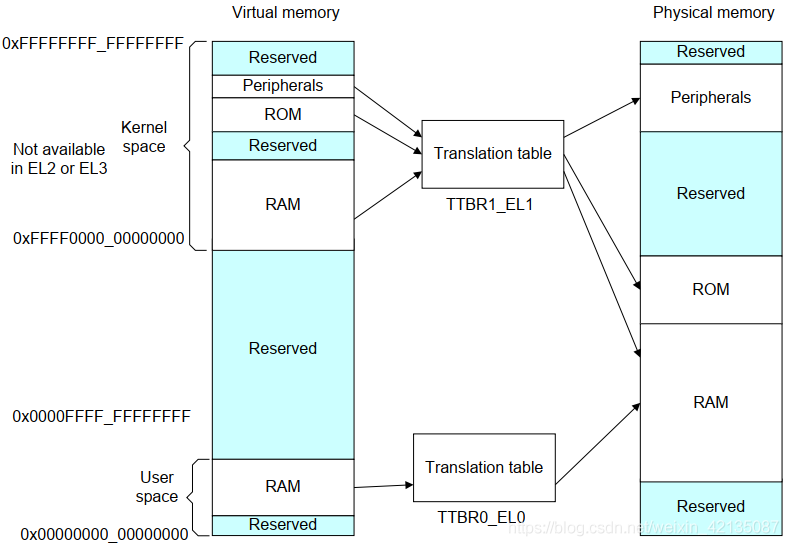

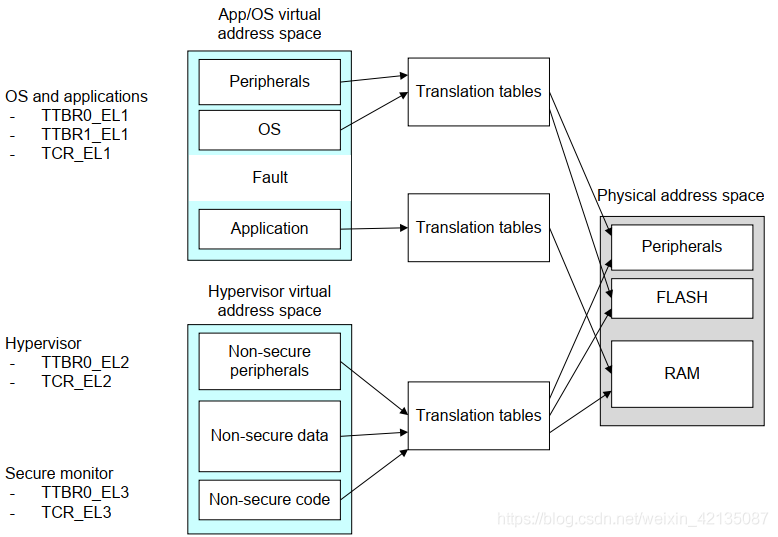

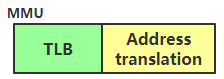

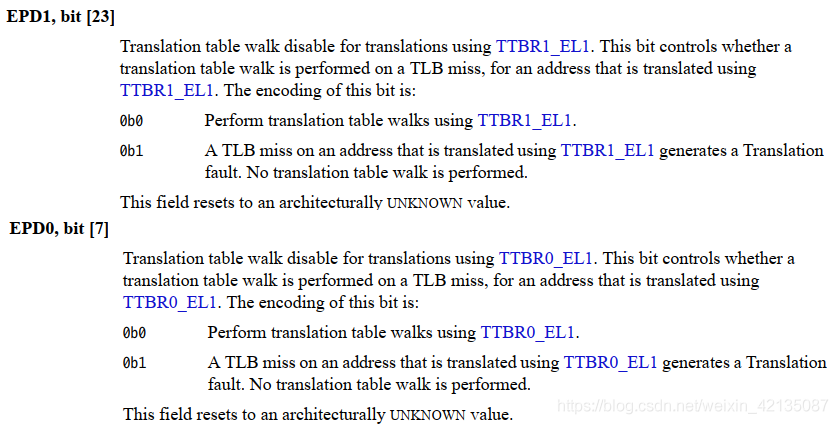

下图是一个linux kernel系统中宏观的虚拟地址到物理地址转换的视图,可以看出在MMU进行地址转换时,会依赖TTBRx_EL1寄存器指向的一个页表基地址。其中,TTBR1_EL1指向特权模式的页表基地址,用于特权模式下的地址空间转换;TTBR0_EL0指向非特权模式的页表基地址,用于非特权模式下的地址空间转换。刚刚我们也提到,CPU发出读写后, MMU会自动的将虚拟地址转换为为例地址,那么我们软件需要做什么呢?我们软件需要做的其实就是管理这个页表,按照ARM的技术要求去创建一个这样的页表,然后再将其基地址写入到TTBR1_EL1或TTBR0_EL1。当然,根据实际的场景和需要,这个基地址和页表中的内容都会发生动态变化。例如,两个user进程进行切换时,TTBR0_EL1是要从一个user的页表地址,切换到另外一个user的页表地址。

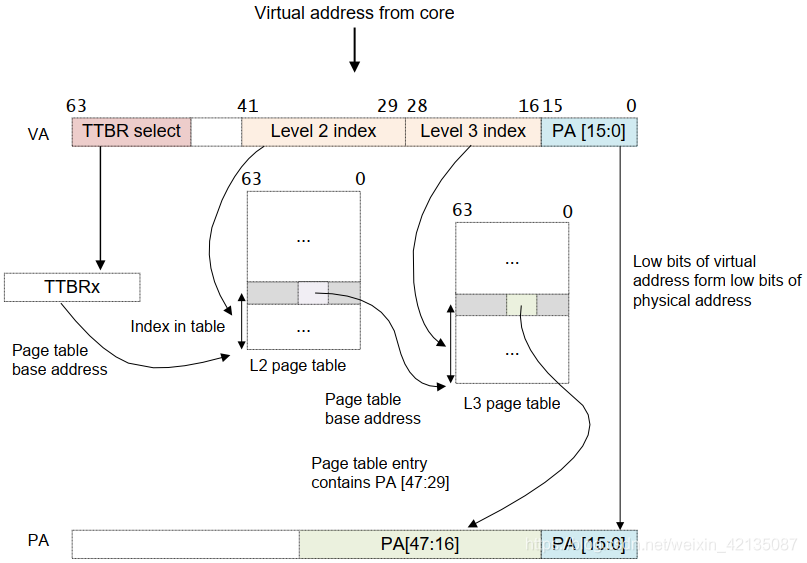

MMU地址翻译的过程

using a 64KB granule with a 42-bit virtual address space,地址翻译的过程(只用到一级页表的情况):

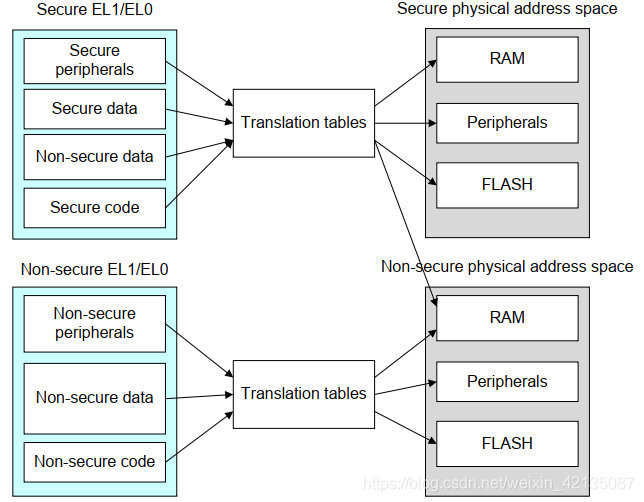

在secure和non-secure中使用MMU

TTBRx_EL1是banked的,在linux和optee双系统的环境下,可同时开启两个系统的MMU。在secure和non-secure中使用不同的页表.secure的页表可以映射non-secure的内存,而non-secure的页表不能去映射secure的内存,否则在转换时会发生错误。

在不同异常等级中使用MMU

在ARMV8-aarch64架构下,页表基地址寄存器有:

- TTBR0_EL1 – banked

- TTBR1_EL1 – banked

- TTBR1_EL2

- TTBR1_EL3

在EL0/EL1的系统中,MMU地址转换时,如果虚拟地址在0x00000000_ffffffff - 0x0000ffff_ffffffff范围,MMU会自动使用TTBR0_EL1指向的页表,进行地址转换;如果虚拟地址在0xffff0000_ffffffff - 0xffffffff_ffffffff范围,MMU会自动使用TTBR1_EL1指向的页表,进行地址转换。

在EL2系统中,MMU地址转换时,会自动使用TTBR2_EL1指向的页表。

在EL3系统中,MMU地址转换时,会自动使用TTBR3_EL1指向的页表

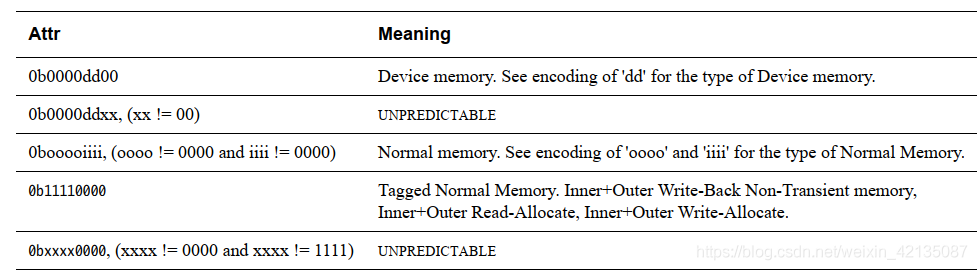

memory attributes介绍

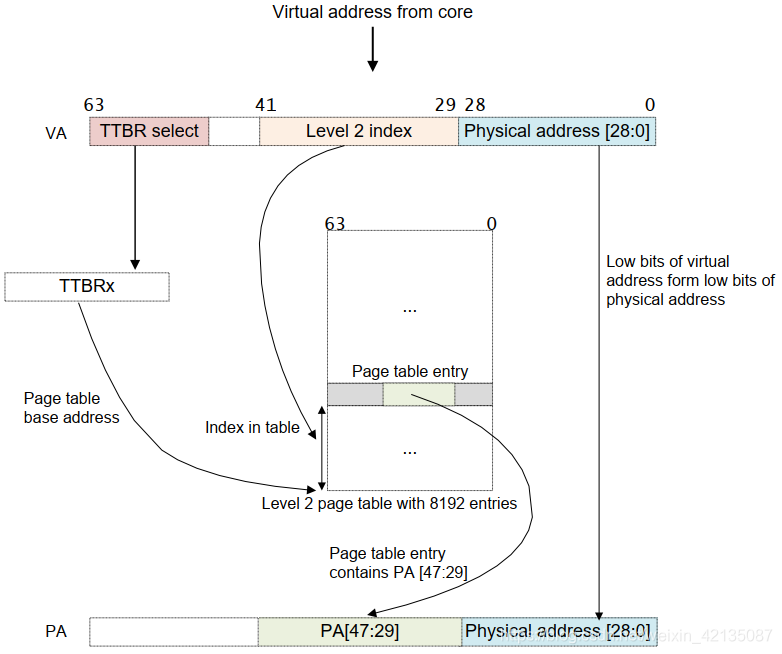

translation tables为每一块region(entry)都定义了一个memory attributes条目,如同下面这个样子(以linux kernel为例,在创建页表的时候,应该会设置这个memory attributes,有待看代码去验证):

在这块region(entry)的memory attributes条目中的BIT4:2(index)指向了系统寄存器MAIR_ELn中的attr,MAIR_ELn共有8中attr选择。

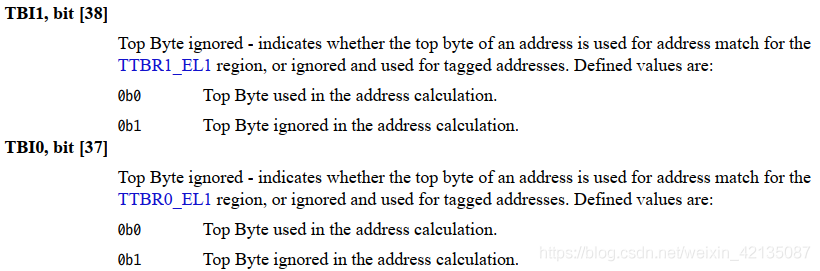

memory tagging介绍

When tagged addressing support is enabled, the top eight bits [63:56] of the virtual address are ignored by the processor. It internally sets bit [55] to sign-extend the address to 64-bit format. The top 8 bits can then be used to pass data. These bits are ignored for addressing and translation faults. The TCR_EL1 has separate enable bits for EL0 and EL1

如果使用memory tagging, 虚拟地址的[63:56]用于传输签名数据,bit[55]表示是否需要签名.TCR_EL1也会有一个bit区分是给EL0用的还是给EL1用的

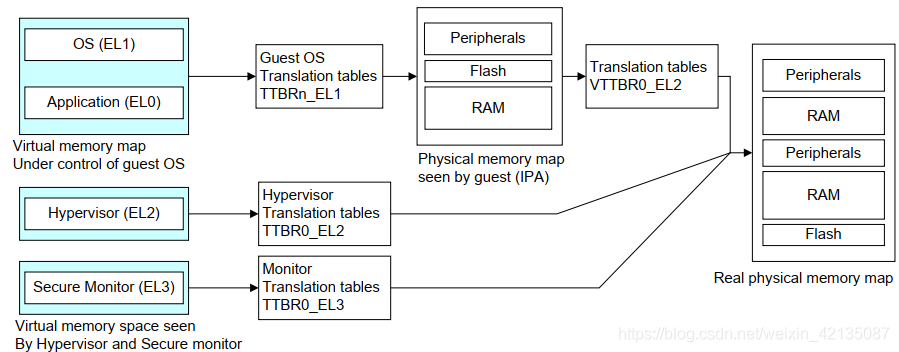

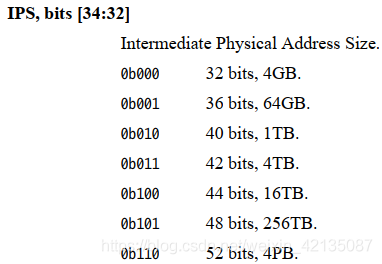

启用hypervisor

如果启用了hypervisor那么虚拟地址转换的过程将有VA—>PA变成了VA—>IPA—>PA, 也就是要经过两次转换.在guestos(如linux kernel)中转换的物理地址,其实不是真实的物理地址(假物理地址),然后在EL2通过VTTBR0_EL2基地址的页表转换后的物理地址,才是真实的硬件地址。

IPA : intermediate physical address

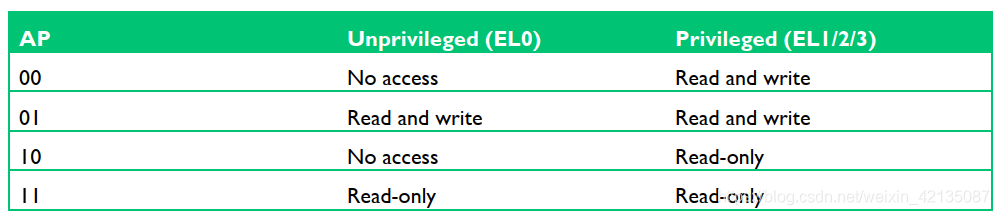

Access permissions

Access permissions are controlled through translation table entries. Access permissions control whether a region is readable or writeable, or both, and can be set separately to EL0 for unprivileged and access to EL1, EL2, and EL3 for privileged accesses, as shown in the following table

参考 :SCTLR_EL1.WXN、SCTLR.UWXN

- non-executable (Execute Never (XN))

- The Unprivileged Execute Never (UXN)

- Privileged Execute Never (PXN)

MMU/cache相关的寄存器总结

MMU(address translation /TLB maintenance)、cache maintenance相关的寄存器

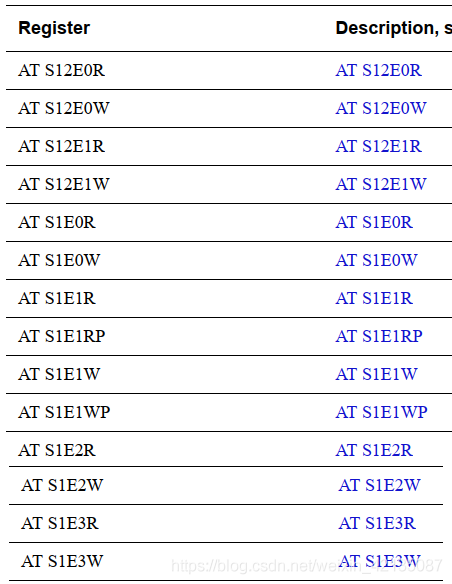

- address translation

address translation 共计14个寄存器

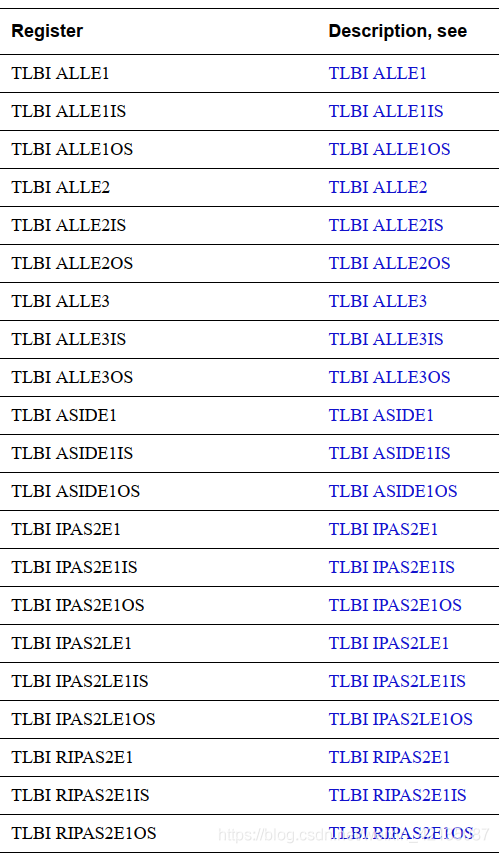

2 . TLB maintenance

TLB maintenance数十个寄存器

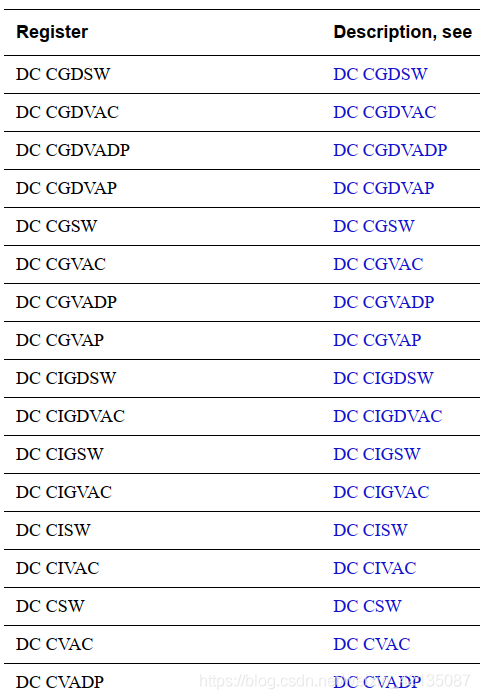

3 . cache maintenance

4 . Base system registers

系统寄存器中, 和MMU/Cache相关的寄存器有:

TTBR0_ELx TTBR1_ELx

(aarch64)

- TTBR0_EL1

- TTBR0_EL2

- TTBR0_EL3

- TTBR1_EL1

- VTTBR_EL2

(aarch32)

- TTBR0

- TTBR1

- HTTBR

- VTTBR

TCR_ELx

(aarch64)

- TCR_EL1

- TCR_EL2

- TCR_EL3

- VTCR_EL2

(aarch32)

- TTBCR(NS)

- HTCR

- TTBCR(S)

- VTCR

MAIR_ELx

- MAIR_EL1

- MAIR_EL2

- MAIR_EL3

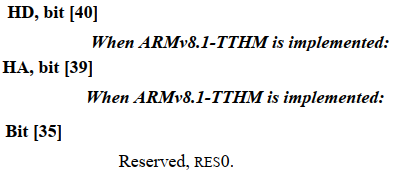

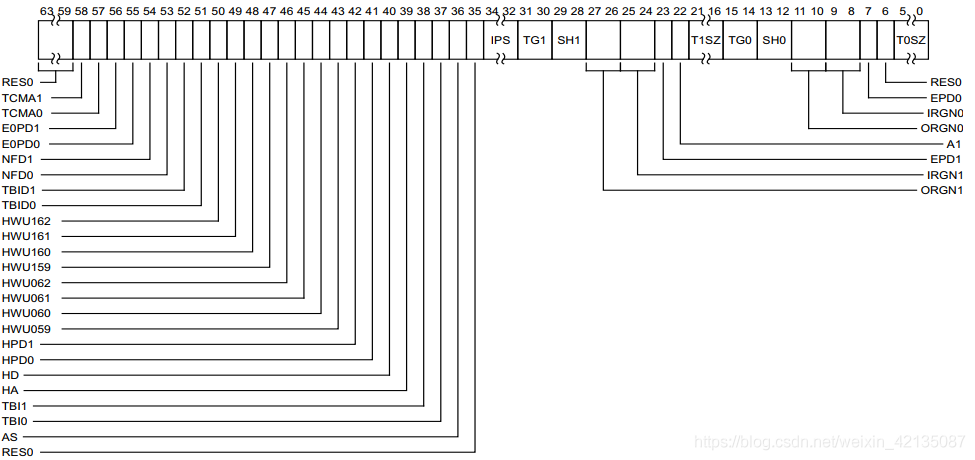

系统寄存器 — TCR寄存器介绍

在ARM Core中(aarch64),还有几个相关的系统寄存器:

- TCR_EL1 banked

- TCR_EL2

- TCR_EL3

- T1SZ、T0SZ

- T1SZ, bits [21:16] 通过TTBR1寻址的内存区域的大小偏移量,也就是TTBR1基地址下的一级页表的大小

- T0SZ, bits [5:0]

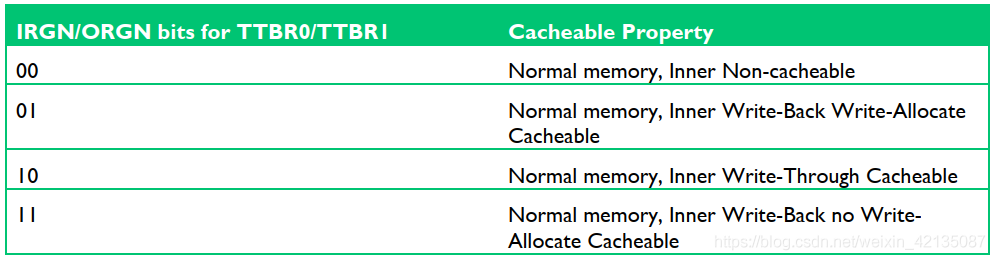

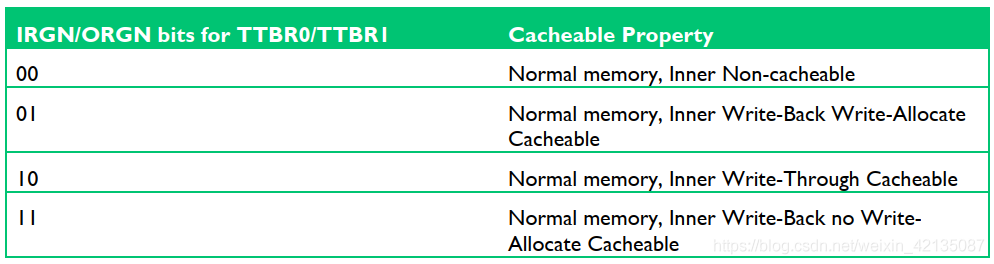

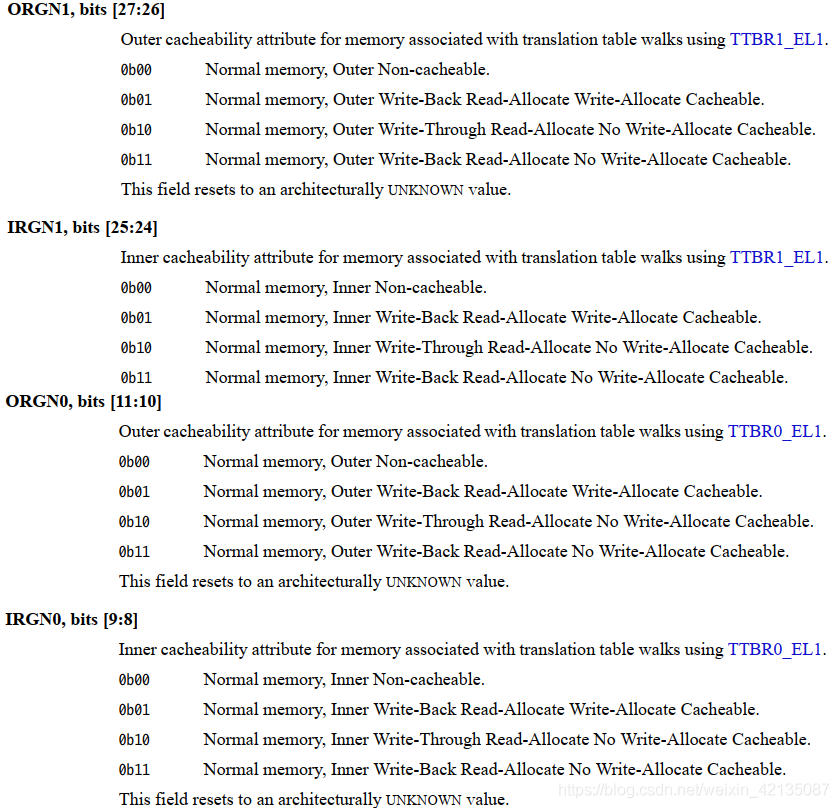

2 . ORGN1、IRGN1、ORGN0、IRGN0

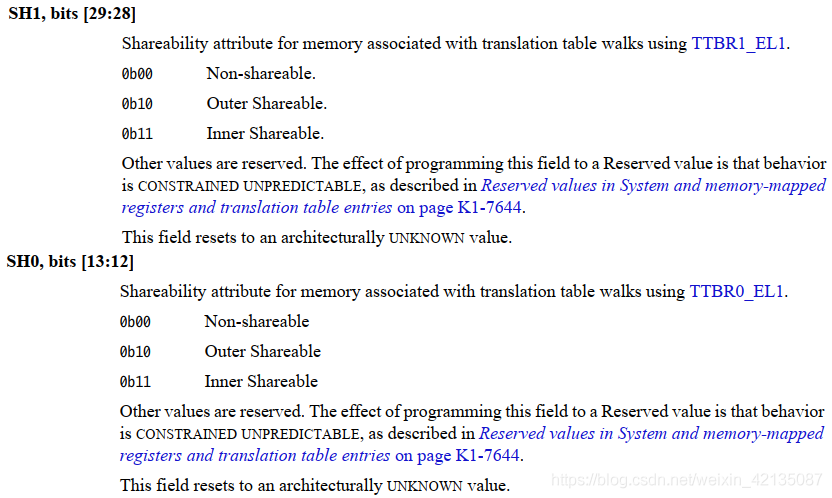

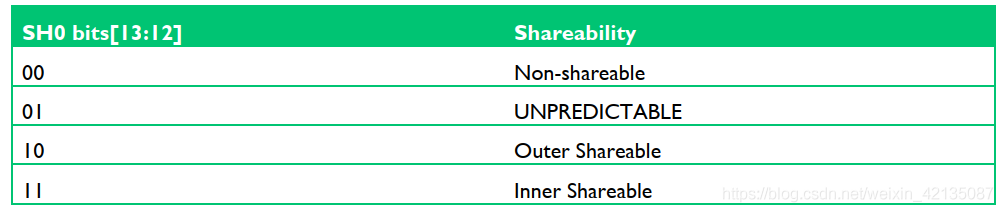

3 . SH1、SH0

对于Inner和Outer Shareable,有个简单的的理解,就是认为他们都是一个东西。在最近的ARM A系列处理器上上,配置处理器RTL的时候,会选择是不是把inner的传输送到ACE口上。当存在多个处理器簇或者需要双向一致性的GPU时,就需要设成送到ACE端口。这样,内部的操作,无论inner shareable还是outershareable,都会经由CCI广播到别的ACE口上。

4 . TG0/TG1 - Granule size

代码使用示例展

设置inner/outer cache的属性(只写模式/回写模式/write allocate/No-write allocate)

#define TCR_IRGN_WBWA ((UL(1) << 8) | (UL(1) << 24)) //使用TTBR0和使用TTBR1时后的inner cache的属性设置

#define TCR_ORGN_WBWA ((UL(1) << 10) | (UL(1) << 26)) //使用TTBR0和使用TTBR1时后的outer cache的属性设置

#define TCR_CACHE_FLAGS TCR_IRGN_WBWA | TCR_ORGN_WBWA // inner + outer cache的属性值

ENTRY(__cpu_setup)

......

/*

* Set/prepare TCR and TTBR. We use 512GB (39-bit) address range for

* both user and kernel.

*/

ldr x10, =TCR_TxSZ(VA_BITS) | TCR_CACHE_FLAGS | TCR_SMP_FLAGS | \

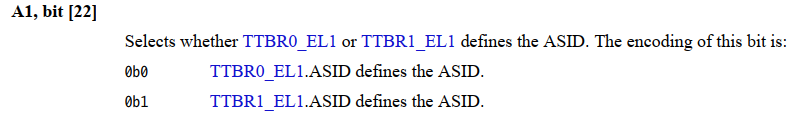

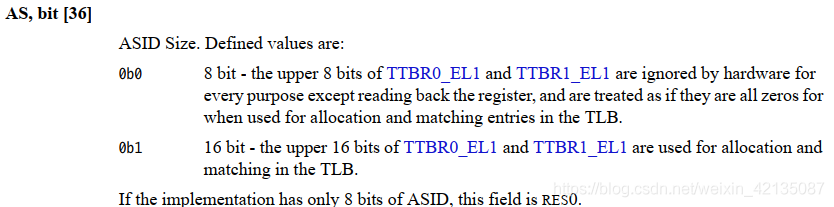

TCR_TG_FLAGS | TCR_ASID16 | TCR_TBI0 | TCR_A1

tcr_set_idmap_t0sz x10, x9

......

msr tcr_el1, x10

ret // return to head.S

ENDPROC(__cpu_setup)属性设置了1,也就是回写模式、write allocate模式。