深入了解 CPU 的型号、代际架构与微架构

在10月16号的时候,Intel 正式发布了第 14 代的酷睿处理器。但还有很多同学看不懂这种发布会上发布的各种 CPU 参数。借着这个时机,我给大家深入地讲讲 CPU 的型号规则、代际架构与微架构方面的知识。

CPU 在整个计算机硬件中、技术体系中都算是最最重要的东西了。但很遗憾的是,80%以上的开发同学对 CPU 并不是很了解。所以在前面的文章中,我带领大家深入地学习了很多内核中管理和调度 CPU 资源相关的文章。在今天,我从 CPU 硬件相关的技术细节切入,带领大家更好地认识 CPU。

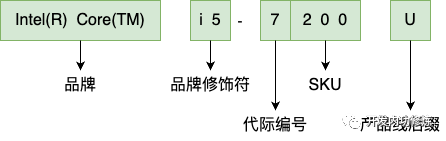

在本文中,我以手头有一台之前用过的 ThinkPad x270 的笔记本电脑举例。在这台电脑中的 CPU 型号是 Intel(R) Core(TM) i5-7200U CPU @ 2.50GHz 2.71 GHz。那么这个型号字符串中都隐含了哪些技术信息呢?今天,就让我们以这个型号为切入点,深入地了解个人 PC 电脑中 CPU 硬件相关的技术点。

一、Intel 的 CPU 型号规则

无论是哪家 CPU 厂商,为了更好地管理自己生产的众多型号的产品,也为了能更好地让消费者对自己家的产品快速地了解。都会定义一套产品规则。对于 Intel 来说,它的命令规则大致如下:

Intel 把 CPU 的编号分成了品牌标志、品牌修饰符、代际编号、SKU、产品线后缀五个部分。接下来我们分别展开对这五个部分来了解。第一部分是品牌标志。最最常见的 x86 CPU 品牌包括 Intel 和 AMD 两家公司。而 Intel 又面向不同的市场需求,包括凌动、赛扬、奔腾、酷睿、至强等多个子品牌。

- 酷睿(CORE)、赛扬(CELERON)、奔腾(PENTIUM)都是应用在家用 PC 电脑上的品牌。其中奔腾和赛扬这两个品牌已经算作是历史了。奔腾在 1992 年推出,之后在很长一段时间里是 PC 家用电脑的主流。赛扬是 1998 年时为了和 AMD 竞争低价市场推出的产品,可以理解为缩水版的奔腾。酷睿是 2006 年推出,直到现在仍然是 PC 电脑里的主流品牌。

- 志强(Xeon)是企业级的CPU,多用于服务器和工作站。大家在工作中使用的线上服务器,基本都是这个子品牌旗下的产品。

- 凌动(Atom)主打省电和低功耗,主要用在手机平板等设备上。是的,Intel 也是做过手机 CPU 的,但因为功耗问题在竞争中被 arm 架构各家处理器厂商打败,在 2016 年后逐渐退出市场。

第二部分是品牌修饰符。这个部分是为了区分处理器的市场定位的,一般来说同一年代生产的 CPU 中, i3 i5 i7 i9 的性能是依次递增的。分别代表着低端、中端和高端的定位。

第三部分是 CPU 的代际编号。这一部分有可能是一位数字,也有可能是两位的数字。在我们举例的这颗 CPU 上,代际编号是“7”。这个代际编号对应的是 Intel 于 2016 年推出的内部代号为“Kaby Lake” 的 CPU架构。一般来说,CPU 代际编号越大,则代表架构推出的时间点越新。单核的性能也会更好。关于“Kaby Lake” 后面我们还会单独介绍。

第四部分是 SKU 编号。这是 CPU 厂商为了方便对所有的产品进行库存管理而制定的编号。这类似于超市里商品的条形码、图书的 ISBN 号,方便查询和管理产品的库存量。一般来说,这个值也是越大性能越好,但不绝对。

第五部分是产品线后缀。在笔记本电脑中,H代表的是高性能、U系列代表的是较低功耗、Y系列代表的是极低的功耗。在台式机中,X代表的是最高性能、K代表的是高性能、T代表的是功耗优化。

关于型号规则大家也可以参考 Intel 的官网介绍(https://www.intel.cn/content/www/cn/zh/processors/processor-numbers.html)。

现在我们再回头来看一下我们开头提到的 CPU,Intel(R) Core(TM) i5-7200U CPU。这里面包含的含义就是,这是一个Intel 的酷睿子品牌的 CPU,i7代表着中高端,代际编号是7,这个代际的处理器架构是 2016 年发布的采用的 Kaby Lake 架构生产的。SKU 编号是 200。产品线后缀的 U 代表的是低功耗,比较省电,同时也就代表着性能并不是最强的。

在看最新的发布的酷睿 CPU 型号有,Intel(R) Core(TM) i9-14900K、Intel(R) Core(TM) i7-14700K、Intel(R) Core(TM) i5-14600K 等几款 CPU。这里面也表示了还是属于 Intel 酷睿 子品牌下的产品。i9、i7、i5分别代表着每个 CPU 的档次。14 代表的是代际。900、700、600 属于 SKU 编号。

二、CPU 的代际

前面在看到 Kaby Lake 的时候,肯定很多小伙伴都会表示看不懂这是什么意思。所以这里专门准备一个小节来解释下。前面我们提到每个 CPU 型号中都包含了一个代际编号。比如第 7 代、第 8 代,就在刚刚 2023 的 10 月 16 日,已经更新到了第 14 代。

这个代际代表的 CPU 的生产年份不同、生产工艺不同、架构设计的不同。各个代际除了这个数字的编号外,还会有一个英文代号。比如第 7 代的代际编号就是 Kaby Lake。最新的第 14 代的代际编号是 Raptor Lake Refresh。下表是我搜集整理到的各个代际的信息(在手机上看需要往右拖动一下表格才能够看全)。

| 时间 | 代数 | CPU代际 | 制程工艺 | 微架构 |

|---|---|---|---|---|

| 2013 | 第4代 | Haswell | 22nm | Haswell |

| 2014 | 第5代 | Broadwell | 14nm | Haswell |

| 2015 | 第6代 | Skylake(client) | 14nm | Skylake |

| 2016 | 第7代 | Kaby Lake | 14nm | Skylake |

| 2017 | 第8代 | Coffee Lake | 14nm | Skylake |

| 2018 | 第9代 | Coffee Lake Refresh | 14nm | Skylake |

| 2019 | 第10代 | Ice Lake(client) | 10nm | Sunny Cove |

| 2020 | 第11代 | Tiger Lake | 10nm | Willow Cove |

| 2021 | 第12代 | Alder Lake S | 7nm | 大核Golden Cove 小核Gracemont |

| 2022 | 第13代 | Raptor Lake | 7nm | 大核Raptor Cove 小核Gracemont |

| 2023 | 第14代 | Raptor Lake Refresh | 7nm | 大核Raptor Cove 小核Gracemont |

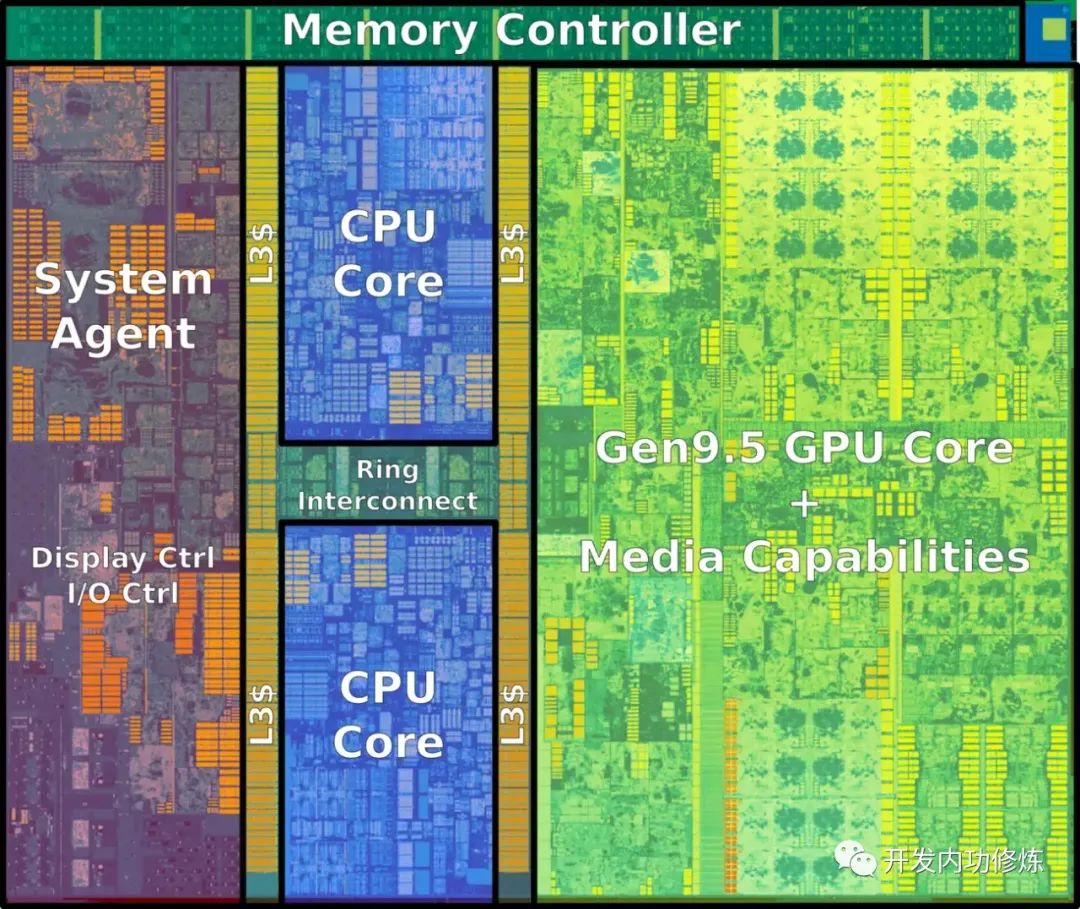

在 Die图中,最上方的Memory Controller 是内存控制器。当前 CPU 能支持什么样规格的内存,以及能支持多大的内存,都是由 CPU 中的内存控制器来决定的。其中 Kaby Lake 的内存控制器相比上一代 Skylake 来说,将支持的内存频率从 DDR4-2133 提升到了 DDR4-2400。下方中间位置是两个物理核,这是 CPU 中最重要的部分。还有两块 L3 Cache,要注意的是虽然在硬件上是有两块 L3,但不管有几块,所有的 L3 缓存都是所有核共享的。 在CPU 的下方最右侧的 Gen9.5 是 CPU 中集成显卡。因为我们不打算深入讲显卡,所以这里大家只要知道 PC 电脑的 CPU 里是包含一块集成显卡的就够了。对这块显卡感兴趣的同学可以移步 https://en.wikichip.org/wiki/intel/microarchitectures/gen9。

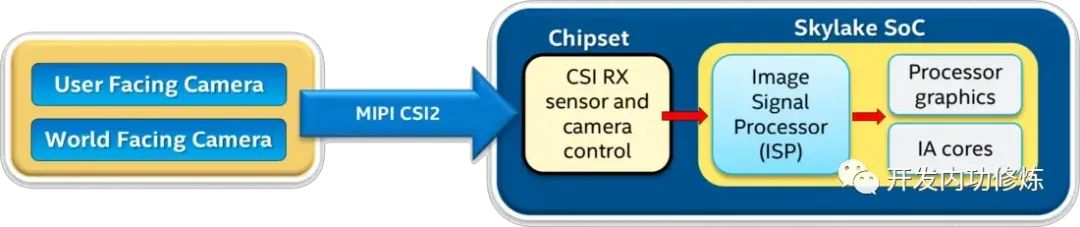

在 CPU 的下方最左侧是 System Agent 模块。在该模块中主要包括外围组件快速互联(Peripheral Component Interconnect Express,简称PCIe) 通道、图像处理单元(Image Processing Unit,IPU)等在 Kaby Lake 中包含 20 个 PCIe 通道。其中有的通道是用于和显卡通信,有的是通过南桥和硬盘、网卡等设备通信。

南桥芯片是用于帮助 CPU 和外围设备交互的。固态硬盘、机械硬盘、网卡等 IO 设备一般来说都是通过南桥来和 CPU 相连的。南桥会收集好了这些设备上的数据再传输给 CPU 处理。另外现在有些高性能的固态硬盘也是直接通过 PCIe 通道和 CPU 通信,这样的硬盘性能更好。

另外 IPU 的功能是支持视频录制成像、人脸检测识别等图像相关处理的硬件支持。

以上就是 Kaby Lake 架构下 CPU 的主要物理结构。另外从表中还可以看到 Kaby Lake 是2016年发布的,制程工艺是 14 nm。CPU 的制程工艺一直在进步,从 2013 年的 22 nm 逐步发展到了今天的 7 nm。制程工艺的进步带来的好处主要是能效比的提升,单位面积上晶体管的数量增加了,但是需要的能耗却变低了。(本文来自于公众号「开发内功修炼」)

至于说其它的代际的架构中的内存控制器、PCIe 通道的变化情况,我们后面再单独写一篇文章。

三、物理核微架构设计

另外每个代际的 CPU 还有个非常不同的地方在于微架构的不同。微架构指的是每个物理核设计时采用的技术方案。不同的微架构对核的设计是不同的,比如 TLB、L1、L2 等各种缓存,再比如 CPU 核内部的运算单元都会有所不同。

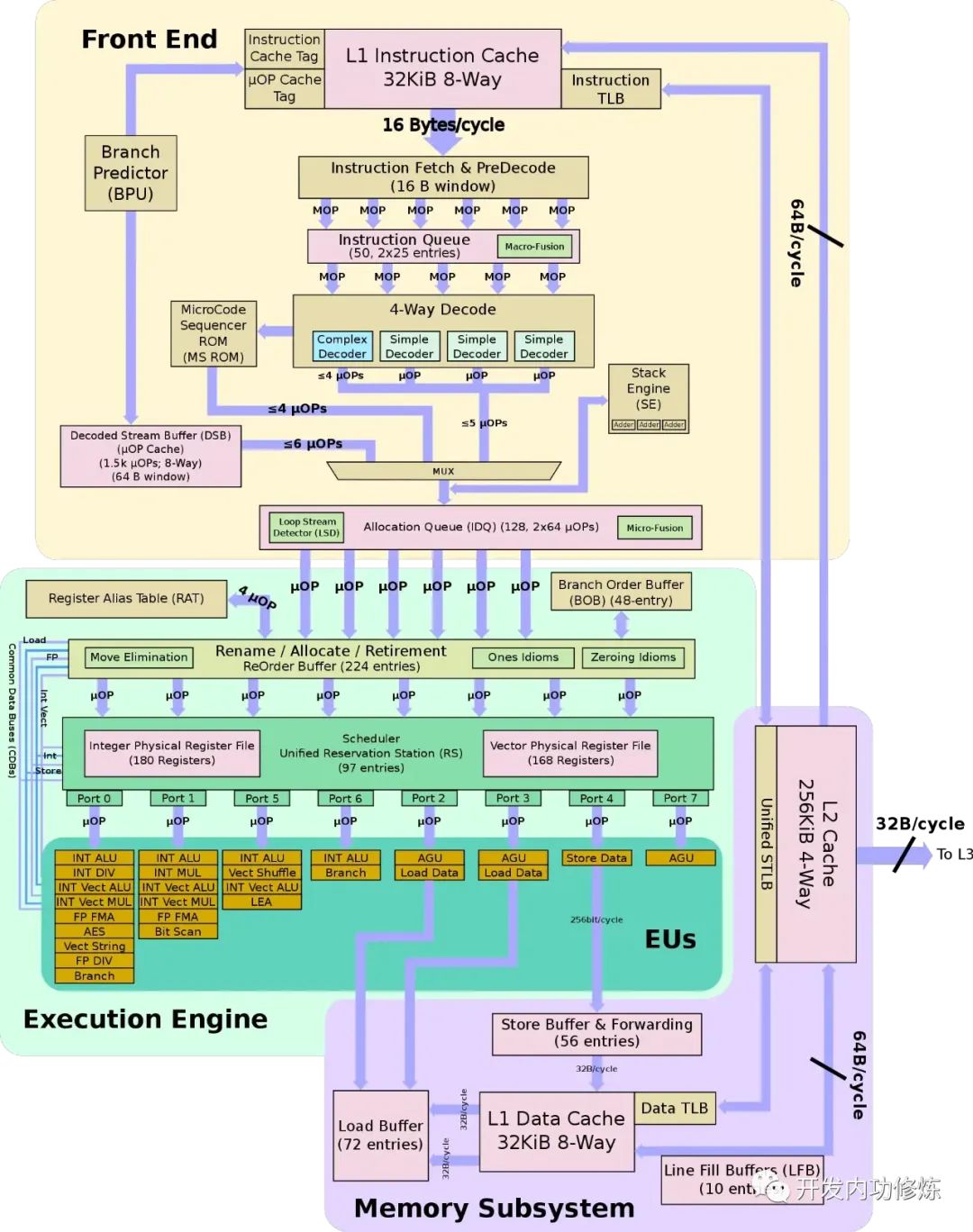

通过上一节中的表格,可以看到我手头的这颗Intel(R) Core(TM) i5-7200U CPU 代际编号为Kaby Lake,微架构的设计仍然沿用的是 Skylake 中的核设计。那么 Skylake 中的物理核是怎么设计的呢?我从官网站到了它的内部物理结构。

上面的图中大致可以根据颜色的不同分成三大块区域。第一块区域是黄色部分的前端,也叫 Front End。

前端部分的作用是从内存中获取指令并解码,然后把解码后的指令放到队列中,等待 CPU 后端处理。还包括了 CPU 中的分支预测的实现 BPU。另外也还包含解析指令是需要用到的 L1 指令缓存和指令 TLB。

其中从上图中也可以看到,Skylake 核中的 L1 指令缓存的大小是 32 KiB。

第二块区域是绿色的后端,又叫 Execution Engine。

后端模块的作用是从队列中获取前端解码好了的指令开始运行。在后端中包括 Port0、Port1、...、Port7 等 8 个端口。每个端口都支持不同的微操作(uOP)的处理。

其中 Port0、Port1、Port5、Port6支持整数、浮点数的加法运算,Port2、Port3 用于地址生成和加载,Port4用于存储操作。每个

因为有 8 个 Port,所以后端在一个时钟周期内,是可以最多处理 8 个微操作的。

第三块区域是紫色的存储系统,又叫 Momory SubSystem。

在这里包括了 L1 级别的 Data 缓存区,图中也展示了它的大小是 32KiB。还包括 L2 缓存,其大小是 256 KiB。另外还有 Data TLB 等缓存。这些缓存都是位于 CPU 核内部的。访问它们的速度比访问内存更快。(本文来自于公众号「开发内功修炼」)

不同代际的 CPU 的微架构设计也是不同的,单核性能也会有变化,后面的文章里我们再讲。

总结

今天借助我手头的一枚老旧的 CPU Intel(R) Core(TM) i5-7200U CPU @ 2.50GHz 2.71 GHz。咱们深入地介绍了 Intel 的 CPU 命名规则。了解了命名规则有助于你快速判断一颗 CPU 的大概的性能。不过如果你是一名发烧友,还是建议你搜索天梯图来了解每个 CPU 的排名情况。

另外我们也找到了这颗 CPU 的硬件解剖图 - Die 图。从 Die 图里我们直观地看到了 CPU 内部的物理结构。在 i5-7200U 中包括了集成显卡、包括了物理核、还看到了 L3 缓存的位置。另外内存控制器也是集成在 CPU 的,CPU 就是通过它来和内存通信的。还有就是 PCIe 通道,是 CPU 用来和硬盘、网卡、显卡等设备通信的通路。

最后我们深入到了 Skylake 的物理核的内部。了解到了物理核中的三大组成部分:前端、后端和存储模块。其中前端负责指令的解析,后端负责指令解析后的微操作的运行处理。存储系统为前端和后端提供了 L1、L2 等缓存,用于加速内存访问。

看到这里,相信你对 CPU 会有更深刻的认识了。后面我们再来一篇文章介绍不同代际中都在哪些地方有进步。别犹豫,快把本文快分享给你的好基友吧!